| <b>FAIRCI</b><br>SEMICOND                                                                                  |                                                                                                                                    |                                                                                                                    | October 1987<br>Revised January 1999                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Do<br>The MM74C14 H<br>mentary MOS (C<br>N- and P-channe<br>and negative goi<br>low variation with | mitt Trigge<br>escription<br>MOS) integrated circuit<br>el enhancement transis<br>g threshold voltages V<br>respect to temperature | nonolithic comple-<br>t constructed with<br>stors. The positive<br>$T_+$ and $V_{T-}$ , show<br>e (typ. 0.0005V/°C | All inputs are protected from damage due to static dis-<br>charge by diode clamps to V <sub>CC</sub> and GND.<br><b>Features</b><br>Wide supply voltage range: 3.0V to 15V<br>High noise immunity: 0.70 V <sub>CC</sub> (typ.) |

| anteed.                                                                                                    | d hysteresis, V <sub>T+</sub> – V <sub>T-</sub>                                                                                    | ≥ 0.2 V <sub>CC</sub> is guar-                                                                                     | <ul> <li>Low power: TTL compatibility:<br/>0.4 V<sub>CC</sub> (typ.) 0.2 V<sub>CC</sub> guaranteed</li> <li>Hysteresis: 0.4 V<sub>CC</sub> (typ.): 0.2 V<sub>CC</sub> guaranteed</li> </ul>                                    |

| Ordering (                                                                                                 |                                                                                                                                    |                                                                                                                    |                                                                                                                                                                                                                                |

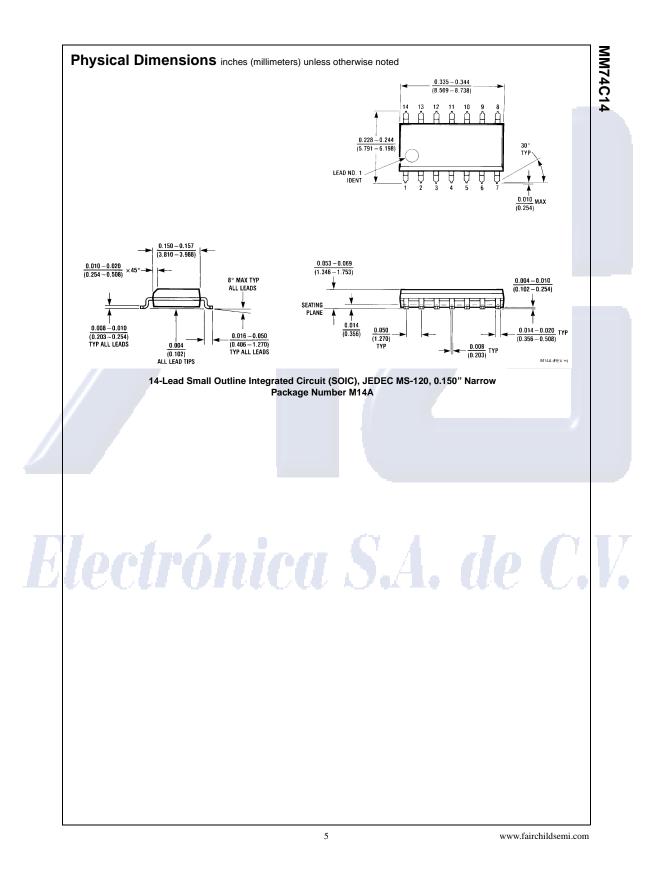

| Order Number<br>MM74C14M                                                                                   | Package Number<br>M14A 14                                                                                                          | 4-Lead Small Outline                                                                                               | Package Description Integrated Circuit (SOIC), JEDEC MS-120, 0.150" Narrow                                                                                                                                                     |

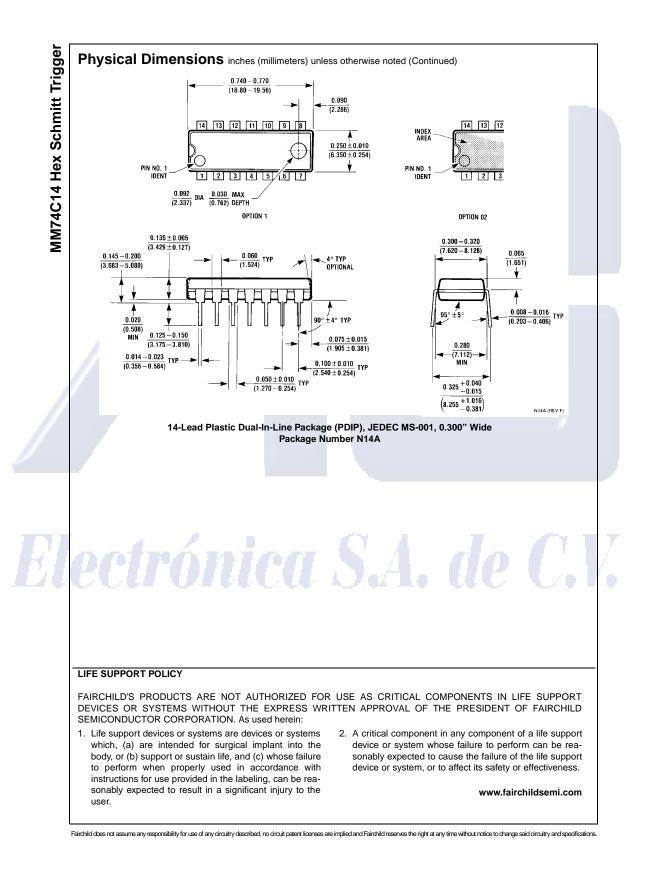

| MM74C14N                                                                                                   |                                                                                                                                    |                                                                                                                    | -Line Package (PDIP), JEDEC MS-001, 0.300" Wide                                                                                                                                                                                |

|                                                                                                            | V                                                                                                                                  | Pin Assignments f                                                                                                  | or DIP and SOIC                                                                                                                                                                                                                |

| lec                                                                                                        |                                                                                                                                    | Pin Assignments f                                                                                                  |                                                                                                                                                                                                                                |

© 1999 Fairchild Semiconductor Corporation DS005879.prf

www.fairchildsemi.com

| <b>~</b> |

|----------|

| U<br>С   |

| 4        |

| ~        |

| Σ        |

| Σ        |

## Absolute Maximum Ratings(Note 1)

Voltage at Any Pin Operating Temperature Range Storage Temperature Range Power Dissipation Dual-In-Line Small Outline Operating  $\mathrm{V}_{\mathrm{CC}}$  Range

-0.3Vto V<sub>CC</sub> + 0.3V -40°C to +85°C -65°C to +150°C 700 mW 500mW 3.0V to 15V

## Absolute Maximum $\mathrm{V}_{\mathrm{CC}}$ Lead Temperature (Soldering, 10 seconds)

18V

260°C

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Tempera-ture Range" they are not meant to imply that the devices should be oper-ated at these limits. The Electrical Characteristics tables provide conditions for actual device operation.

## **DC Electrical Characteristics**

| Symbol                           | Parameter                        | Conditions                                             | Min  | Тур    | Max  | Units |

|----------------------------------|----------------------------------|--------------------------------------------------------|------|--------|------|-------|

| CMOS TO C                        | Mos                              |                                                        | 11   | 1 1    | 7    | 1     |

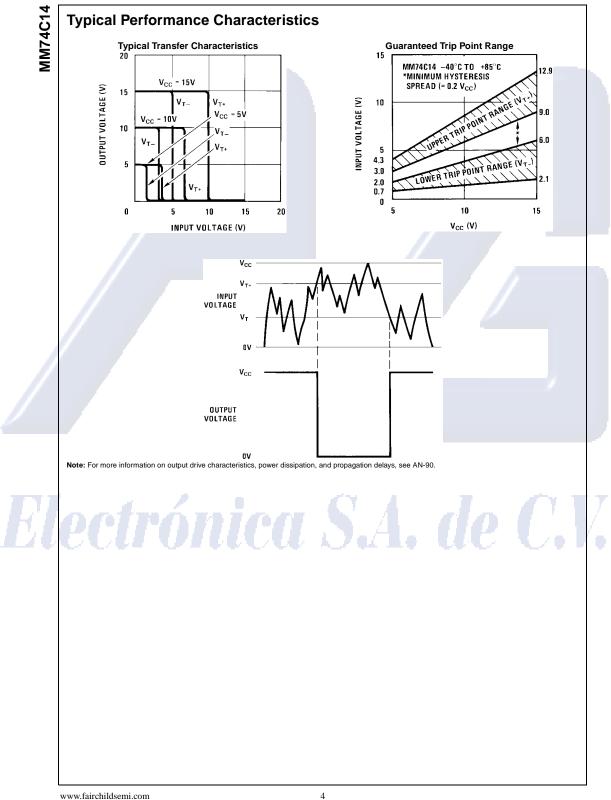

| V <sub>T+</sub>                  | Positive Going Threshold Voltage | $V_{CC} = 5V$                                          | 3.0  | 3.6    | 4.3  | V     |

|                                  |                                  | $V_{CC} = 10V$                                         | 6.0  | 6.8    | 8.6  | V     |

|                                  |                                  | $V_{CC} = 15V$                                         | 9.0  | 10.0   | 12.9 | V     |

| V <sub>T-</sub>                  | Negative Going Threshold Voltage | $V_{CC} = 5V$                                          | 0.7  | 1.4    | 2.0  | V     |

|                                  |                                  | $V_{CC} = 10V$                                         | 1.4  | 3.2    | 4.0  | V     |

|                                  |                                  | V <sub>CC</sub> = 15V                                  | 2.1  | 5.0    | 6.0  | V     |

| V <sub>T+</sub> -V <sub>T-</sub> | Hysteresis                       | $V_{CC} = 5V$                                          | 1.0  | 2.2    | 3.6  | V     |

|                                  |                                  | $V_{CC} = 10V$                                         | 2.0  | 3.6    | 7.2  | V     |

|                                  |                                  | V <sub>CC</sub> = 15V                                  | 3.0  | 5.0    | 10.8 | V     |

| V <sub>OUT(1)</sub>              | Logical "1" Output Voltage       | $V_{CC} = 5V, I_{O} = -10 \ \mu A$                     | 4.5  |        |      | V     |

|                                  | 1                                | $V_{CC} = 10V, I_{O} = -10 \mu A$                      | 9.0  |        |      | V     |

| V <sub>OUT(0)</sub>              | Logical "0" Output Voltage       | $V_{CC} = 5V, I_{O} = 10 \ \mu A$                      |      |        | 0.5  | V     |

|                                  |                                  | $V_{CC} = 10V, I_{O} = 10 \ \mu A$                     |      |        | 1.0  | V     |

| I <sub>IN(1)</sub>               | Logical "1" Input Current        | $V_{CC} = 15V, V_{IN} = 15V$                           |      | 0.005  | 1.0  | μΑ    |

| I <sub>IN(0)</sub>               | Logical "0" Input Current        | $V_{CC} = 15V, V_{IN} = 0V$                            | -1.0 | -0.005 |      | μΑ    |

| I <sub>CC</sub>                  | Supply Current                   | $V_{CC} = 15V, V_{IN} = 0V/15V$                        |      | 0.05   | 15   | μΑ    |

|                                  |                                  | V <sub>CC</sub> = 5V, V <sub>IN</sub> = 2.5V (Note 2)  |      | 20     |      | μΑ    |

|                                  |                                  | V <sub>CC</sub> = 10V, V <sub>IN</sub> = 5V (Note 2)   |      | 200    |      | μΑ    |

|                                  |                                  | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 7.5V (Note 2) |      | 600    |      | μΑ    |

| CMOS/LPTT                        | LINTERFACE                       |                                                        |      |        |      |       |

| V <sub>IN(1)</sub>               | Logical "1" Input Voltage        | $V_{CC} = 5V$                                          | 4.3  |        |      | V     |

| V <sub>IN(0)</sub>               | Logical "0" Input Voltage        | $V_{CC} = 5V$                                          |      |        | 0.7  | V     |

| V <sub>OUT(1)</sub>              | Logical "1" Output Voltage       | 74C, $V_{CC}$ = 4.75V, $I_{O}$ = -360 $\mu$ A          | 2.4  |        |      | V     |

| V <sub>OUT(0)</sub>              | Logical "0" Output Voltage       | 74C, V <sub>CC</sub> = 4.75V, I <sub>O</sub> = 360 μA  |      |        | 0.4  | V     |

OUTPUT DRIVE (see Family Characteristics Data Sheet)  $T_A = 25^{\circ}C$  (Short Circuit Current)

|                                                                                                                         |                       |                                  |       | -    |    |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------|-------|------|----|--|

| ISOURCE                                                                                                                 | Output Source Current | $V_{CC} = 5V, V_{OUT} = 0V$      | -1.75 | -3.3 | mA |  |

|                                                                                                                         | (P-Channel)           |                                  |       |      |    |  |

| ISOURCE                                                                                                                 | Output Source Current | $V_{CC} = 10V, V_{OUT} = 0V$     | -8.0  | -15  | mA |  |

|                                                                                                                         | (P-Channel)           |                                  |       |      |    |  |

| I <sub>SINK</sub>                                                                                                       | Output Sink Current   | $V_{CC} = 5V, V_{OUT} = V_{CC}$  | 1.75  | 3.6  | mA |  |

|                                                                                                                         | (N-Channel)           |                                  |       |      |    |  |

| I <sub>SINK</sub>                                                                                                       | Output Sink Current   | $V_{CC} = 10V, V_{OUT} = V_{CC}$ | 8.0   | 16   | mA |  |

|                                                                                                                         | (N-Channel)           |                                  |       |      |    |  |

| Note 2: Only one of the six inputs is at $\frac{1}{2}$ V <sub>CC</sub> the others are either at V <sub>CC</sub> or GND. |                       |                                  |       |      |    |  |

www.fairchildsemi.com

www.fairchildsemi.com