MC68HC908QY4 MC68HC908QY2 MC68HC908QY2 MC68HC908QY1 MC68HC908QY1 MC68HC908QT1

**Data Sheet**

M68HC08 Microcontrollers

MC68HC908QY4 MC68HC908QY2 MC68HC908QY2 MC68HC908QY1 MC68HC908QY1 MC68HC908QT1

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available.

# **Chapter 1 General Description**

# 1.1 Introduction

The MC68HC908QY4 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is a Complex Instruction Set Computer (CISC) with a Von Neumann architecture. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

**Analog-to-Digital FLASH** Pin **Device Memory Size** Converter Count MC68HC908QT1 1536 bytes 8 pins MC68HC908QT2 8 pins 4 ch, 8 bit 1536 bytes MC68HC908QT4 4096 bytes 4 ch. 8 bit 8 pins MC68HC908QY1 1536 bytes 16 pins 4 ch, 8 bit MC68HC908QY2 1536 bytes 16 pins MC68HC908QY4 4096 bytes 4 ch, 8 bit 16 pins

**Table 1-1. Summary of Device Variations**

# 1.2 Features

## Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

- Trimmable internal oscillator

- 3.2 MHz internal bus operation

- 8-bit trim capability allows 0.4% accuracy<sup>(1)</sup>

- ± 25% untrimmed

- Auto wakeup from STOP capability

- Configuration (CONFIG) register for MCU configuration options, including:

- Low-voltage inhibit (LVI) trip point

- In-system FLASH programming

- FLASH security<sup>(2)</sup>

<sup>1.</sup> The oscillator frequency is guaranteed to ±5% over temperature and voltage range after trimming.

<sup>2.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

## **General Description**

- On-chip in-application programmable FLASH memory (with internal program/erase voltage generation)

- MC68HC908QY4 and MC68HC908QT4 4096 bytes

- MC68HC908QY2, MC68HC908QY1, MC68HC908QT2, and MC68HC908QT1 1536 bytes

- 128 bytes of on-chip random-access memory (RAM)

- 2-channel, 16-bit timer interface module (TIM)

- 4-channel, 8-bit analog-to-digital converter (ADC) on MC68HC908QY2, MC68HC908QY4, MC68HC908QT2, and MC68HC908QT4

- 5 or 13 bidirectional input/output (I/O) lines and one input only:

- Six shared with keyboard interrupt function and ADC

- Two shared with timer channels

- One shared with external interrupt (IRQ)

- Eight extra I/O lines on 16-pin package only

- High current sink/source capability on all port pins

- Selectable pullups on all ports, selectable on an individual bit basis

- Three-state ability on all port pins

- 6-bit keyboard interrupt with wakeup feature (KBI)

- Low-voltage inhibit (LVI) module features:

- Software selectable trip point in CONFIG register

- System protection features:

- Computer operating properly (COP) watchdog

- Low-voltage detection with reset

- Illegal opcode detection with reset

- Illegal address detection with reset

- External asynchronous interrupt pin with internal pullup (IRQ) shared with general-purpose input pin

- Master asynchronous reset pin (RST) shared with general-purpose input/output (I/O) pin

- Power-on reset

- Internal pullups on IRQ and RST to reduce external components

- Memory mapped I/O registers

- Power saving stop and wait modes

- MC68HC908QY4, MC68HC908QY2, and MC68HC908QY1 are available in these packages:

- 16-pin plastic dual in-line package (PDIP)

- 16-pin small outline integrated circuit (SOIC) package

- 16-pin thin shrink small outline package (TSSOP)

- MC68HC908QT4, MC68HC908QT2, and MC68HC908QT1 are available in these packages:

- 8-pin PDIP

- 8-pin SOIC

- 8-pin dual flat no lead (DFN) package

Features of the CPU08 include the following:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- · Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

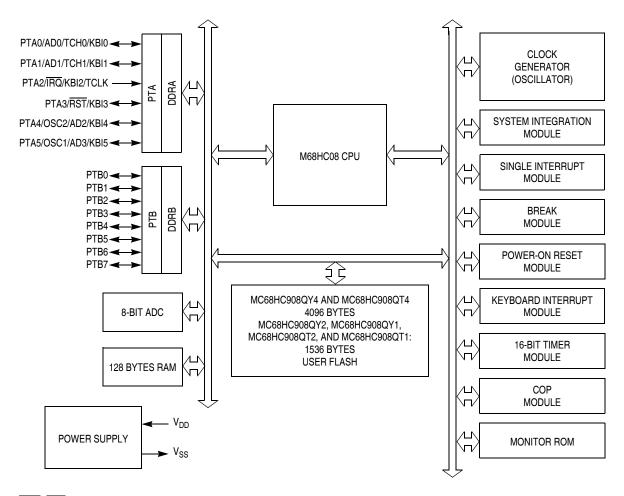

# 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HC908QY4.

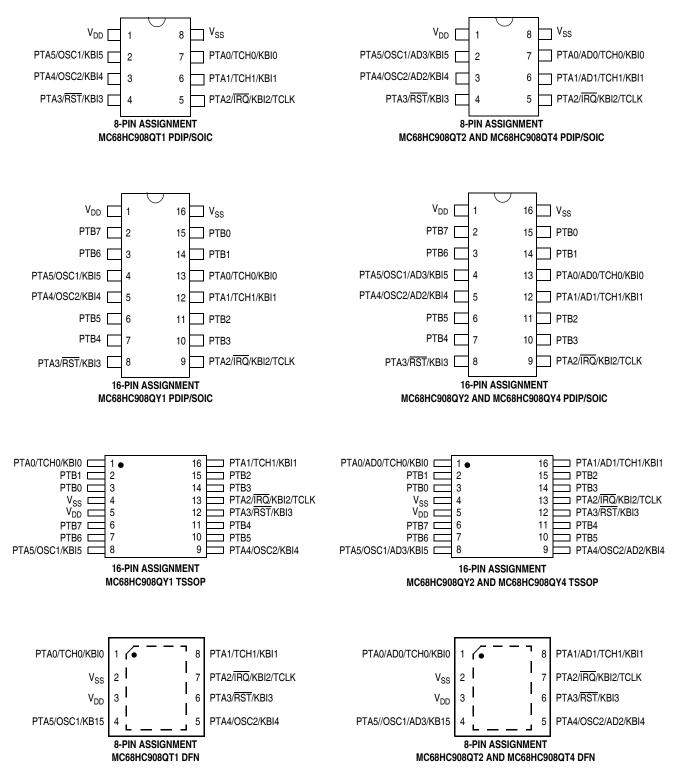

# 1.4 Pin Assignments

The MC68HC908QT4, MC68HC908QT2, and MC68HC908QT1 are available in 8-pin packages and the MC68HC908QY4, MC68HC908QY2, and MC68HC908QY1 in 16-pin packages. Figure 1-2 shows the pin assignment for these packages.

# **General Description**

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HC908QY1 and MC68HC908QT1

Figure 1-1. Block Diagram

Figure 1-2. MCU Pin Assignments

# **General Description**

# 1.5 Pin Functions

Table 1-2 provides a description of the pin functions.

**Table 1-2. Pin Functions**

| Pin<br>Name             | Description                                                                                                      | Input/Output     |

|-------------------------|------------------------------------------------------------------------------------------------------------------|------------------|

| V <sub>DD</sub>         | Power supply                                                                                                     | Power            |

| V <sub>SS</sub>         | Power supply ground                                                                                              | Power            |

|                         | PTA0 — General purpose I/O port                                                                                  | Input/Output     |

| PTA0                    | AD0 — A/D channel 0 input                                                                                        | Input            |

|                         | TCH0 — Timer Channel 0 I/O                                                                                       | Input/Output     |

|                         | KBI0 — Keyboard interrupt input 0                                                                                | Input            |

|                         | PTA1 — General purpose I/O port                                                                                  | Input/Output     |

| PTA1                    | AD1 — A/D channel 1 input                                                                                        | Input            |

| PIAI                    | TCH1 — Timer Channel 1 I/O                                                                                       | Input/Output     |

|                         | KBI1 — Keyboard interrupt input 1                                                                                | Input            |

|                         | PTA2 — General purpose input-only port                                                                           | Input            |

| DTAG                    | IRQ — External interrupt with programmable pullup and Schmitt trigger input                                      | Input            |

| PTA2                    | KBI2 — Keyboard interrupt input 2                                                                                | Input            |

|                         | TCLK — Timer clock input                                                                                         | Input            |

|                         | PTA3 — General purpose I/O port                                                                                  | Input/Output     |

| PTA3                    | RST — Reset input, active low with internal pullup and Schmitt trigger                                           | Input            |

|                         | KBI3 — Keyboard interrupt input 3                                                                                | Input            |

|                         | PTA4 — General purpose I/O port                                                                                  | Input/Output     |

| PTA4                    | OSC2 —XTAL oscillator output (XTAL option only) RC or internal oscillator output (OSC2EN = 1 in PTAPUE register) | Output<br>Output |

|                         | AD2 — A/D channel 2 input                                                                                        | Input            |

|                         | KBI4 — Keyboard interrupt input 4                                                                                | Input            |

|                         | PTA5 — General purpose I/O port                                                                                  | Input/Output     |

| PTA5                    | OSC1 — XTAL, RC, or external oscillator input                                                                    | Input            |

| FIAO                    | AD3 — A/D channel 3 input                                                                                        | Input            |

|                         | KBI5 — Keyboard interrupt input 5                                                                                | Input            |

| PTB[0:7] <sup>(1)</sup> | 8 general-purpose I/O ports                                                                                      | Input/Output     |

<sup>1.</sup> The PTB pins are not available on the 8-pin packages (see note in 12.1 Introduction).

# 1.6 Pin Function Priority

Table 1-3 is meant to resolve the priority if multiple functions are enabled on a single pin.

# NOTE

Upon reset all pins come up as input ports regardless of the priority table.

**Table 1-3. Function Priority in Shared Pins**

| Pin Name | Highest-to-Lowest Priority Sequence                                                             |

|----------|-------------------------------------------------------------------------------------------------|

| PTA0     | $AD0 \rightarrow TCH0 \rightarrow KBI0 \rightarrow PTA0$                                        |

| PTA1     | AD1 $\rightarrow$ TCH1 $\rightarrow$ KBI1 $\rightarrow$ PTA1                                    |

| PTA2     | $\overline{\text{IRQ}} \rightarrow \text{KBI2} \rightarrow \text{TCLK} \rightarrow \text{PTA2}$ |

| PTA3     | $\overline{RST} \to KBI3 \to PTA3$                                                              |

| PTA4     | $OSC2 \to AD2 \to KBI4 \to PTA4$                                                                |

| PTA5     | $OSC1 \to AD3 \to KBI5 \to PTA5$                                                                |

# Chapter 2 Memory

# 2.1 Introduction

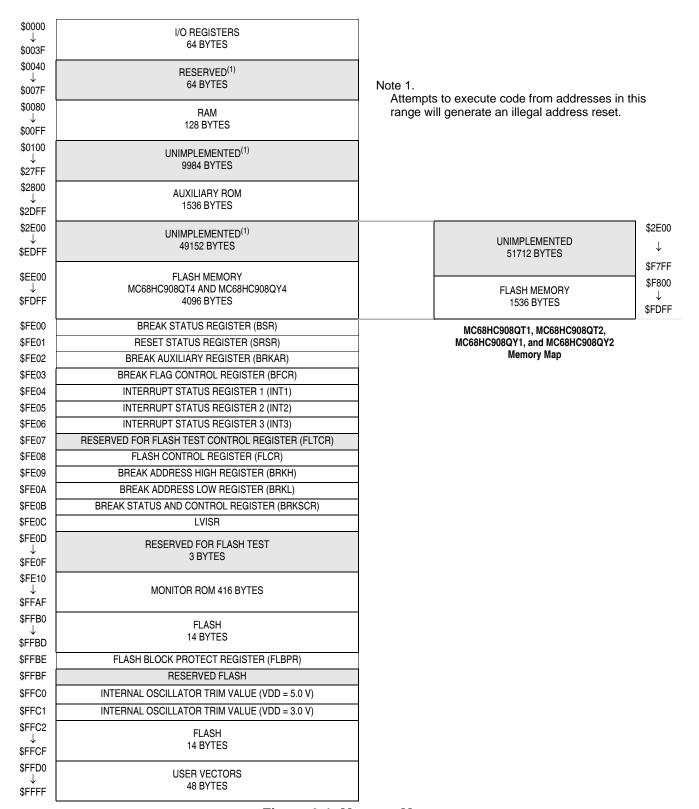

The central processor unit (CPU08) can address 64 Kbytes of memory space. The memory map, shown in Figure 2-1, includes:

- 4096 bytes of user FLASH for MC68HC908QT4 and MC68HC908QY4

- 1536 bytes of user FLASH for MC68HC908QT2, MC68HC908QT1, MC68HC908QY2, and MC68HC908QY1

- 128 bytes of random access memory (RAM)

- 48 bytes of user-defined vectors, located in FLASH

- 416 bytes of monitor read-only memory (ROM)

- 1536 bytes of FLASH program and erase routines, located in ROM

# 2.2 Unimplemented Memory Locations

Accessing an unimplemented location can have unpredictable effects on MCU operation. In Figure 2-1 and in register figures in this document, unimplemented locations are shaded.

# 2.3 Reserved Memory Locations

Accessing a reserved location can have unpredictable effects on MCU operation. In Figure 2-1 and in register figures in this document, reserved locations are marked with the word Reserved or with the letter R.

## Memory

Figure 2-1. Memory Map

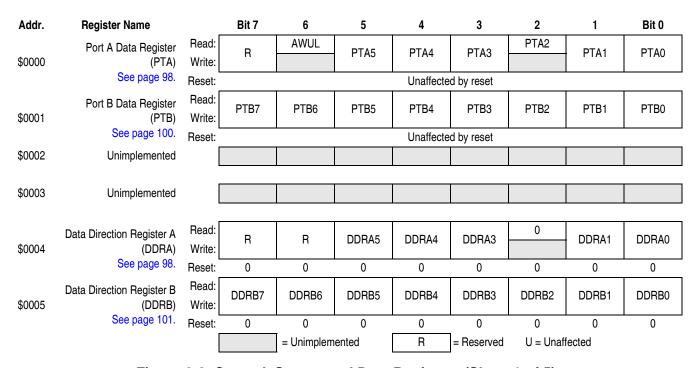

# 2.4 Input/Output (I/O) Section

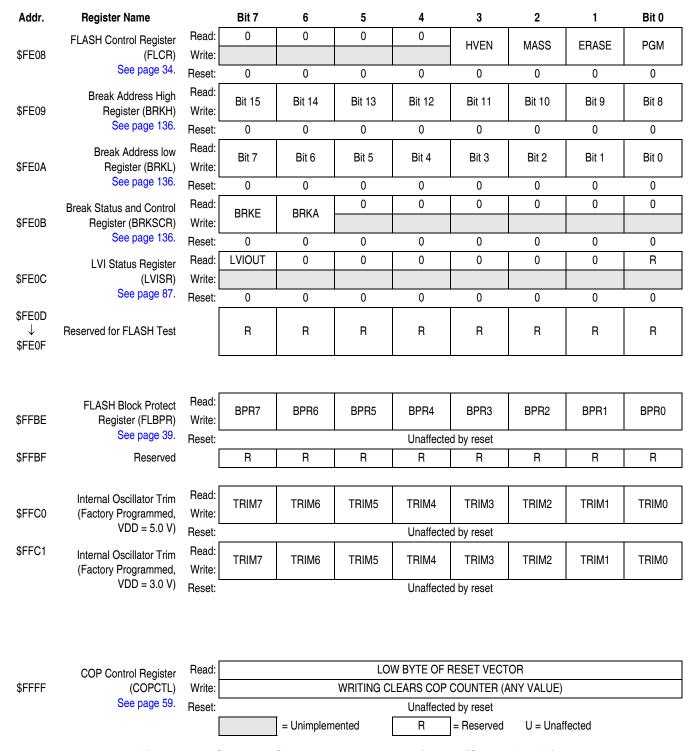

Addresses \$0000–\$003F, shown in Figure 2-2, contain most of the control, status, and data registers. Additional I/O registers have these addresses:

- \$FE00 Break status register, BSR

- \$FE01 Reset status register, SRSR

- \$FE02 Break auxiliary register, BRKAR

- \$FE03 Break flag control register, BFCR

- \$FE04 Interrupt status register 1, INT1

- \$FE05 Interrupt status register 2, INT2

- \$FE06 Interrupt status register 3, INT3

- \$FE07 Reserved

- \$FE08 FLASH control register, FLCR

- \$FE09 Break address register high, BRKH

- \$FE0A Break address register low, BRKL

- \$FE0B Break status and control register, BRKSCR

- \$FE0C LVI status register, LVISR

- \$FE0D Reserved

- \$FFBE FLASH block protect register, FLBPR

- \$FFC0 Internal OSC trim value (factory programmed, VDD = 5.0 V)

- \$FFC1 Internal OSC trim value (factory programmed, VDD = 3.0 V)

- \$FFFF COP control register, COPCTL

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 5)

#### Memory **Register Name** Bit 7 6 5 4 3 2 Bit 0 Addr. 1 Unimplemented \$0006 $\downarrow$ \$000A Unimplemented Read: 0 Port A Input Pullup Enable PTAPUE5 PTAPUE4 PTAPUE3 PTAPUE2 PTAPUE1 PTAPUE0 OSC2EN \$000B Register (PTAPUE) Write: See page 99. 0 0 Reset: 0 0 0 0 0 0 Read: Port B Input Pullup Enable PTBPUE7 PTBPUE6 PTBPUE5 PTBPUE4 PTBPUE3 PTBPUE2 PTBPUE1 PTBPUE0 \$000C Register (PTBPUE) Write: See page 102. Reset: 0 0 0 0 0 0 0 0 \$000D $\downarrow$ Unimplemented \$0019 Read: 0 0 0 0 **KEYF** 0 Keyboard Status and **IMASKK** MODEK \$001A Control Register (KBSCR) Write: **ACKK** See page 83. Reset: 0 0 0 0 0 0 0 0 Read: 0 Keyboard Interrupt **AWUIE** KBIE3 KBIE5 KBIE4 KBIE2 KBIE1 KBIE0 \$001B Enable Register (KBIER) Write: See page 84. 0 0 Reset: 0 0 0 0 0 0 \$001C Unimplemented **IRQF** Read: 0 0 0 0 0 IRQ Status and Control **IMASK** MODE ACK \$001D Register (INTSCR) Write: See page 77. Reset: 0 0 0 0 0 0 0 0 Read: Configuration Register 2 **IRQPUD** OSCOPT1 **IRQEN** R OSCOPT0 R R **RSTEN** \$001E (CONFIG2)<sup>(1)</sup> Write: See page 53. 0(2) Reset: 0 0 0 1. One-time writable register after each reset. 2. RSTEN reset to 0 by a power-on reset (POR) only. Read: Configuration Register 1 **COPRS** LVISTOP LVIRSTD **LVIPWRD** LVI5OR3 **SSREC** STOP COPD (CONFIG1)<sup>(1)</sup> \$001F Write: See page 54. 0(2) Reset: 0 0 0 1. One-time writable register after each reset. 2. LVI5OR3 reset to 0 by a power-on reset (POR) only. Read: **TOF** 0 0 TIM Status and Control TOIE **TSTOP** PS2 PS<sub>1</sub> PS0 0 TRST \$0020 Register (TSC) Write: See page 127. Reset: 0 0 1 0 0 0 0 0

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 5)

Bit 13

0

Bit 12

0

R

Bit 11

0

= Reserved

Bit 10

0

U = Unaffected

Bit 15

0

Read:

Write:

Reset:

TIM Counter Register High

(TCNTH)

See page 128.

\$0021

Bit 14

0

= Unimplemented

Bit 9

0

Bit 8

0

| Addr.                                                 | Register Name                               |                 | Bit 7  | 6          | 5         | 4           | 3              | 2        | 1      | Bit 0    |

|-------------------------------------------------------|---------------------------------------------|-----------------|--------|------------|-----------|-------------|----------------|----------|--------|----------|

| \$0022 TIM Counter Register Low (TCNTL) See page 128. | TIM Counter Register Low                    | Read:           | Bit 7  | Bit 6      | Bit 5     | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0    |

|                                                       | Write:                                      |                 |        |            |           |             |                |          |        |          |

|                                                       | Reset:                                      | 0               | 0      | 0          | 0         | 0           | 0              | 0        | 0      |          |

| \$0023                                                | TIM Counter Modulo<br>Register High (TMODH) | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13    | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8    |

|                                                       | See page 129.                               | Reset:          | 1      | 1          | 1         | 1           | 1              | 1        | 1      | 1        |

| \$0024                                                | TIM Counter Modulo<br>Register Low (TMODL)  | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5     | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0    |

|                                                       | See page 129.                               | Reset:          | 1      | 1          | 1         | 1           | 1              | 1        | 1      | 1        |

|                                                       | TIM Channel 0 Status and                    | Read:           | CH0F   | OLINE      | MOOD      | 14004       | EL COD         | EL 004   | TO1/0  | OLIONANY |

| \$0025                                                | Control Register (TSC0)                     | Write:          | 0      | CH0IE      | HOIE MSOB | MS0A        | ELS0B          | ELS0A    | TOV0   | CH0MAX   |

|                                                       | See page 130.                               | Reset:          | 0      | 0          | 0         | 0           | 0              | 0        | 0      | 0        |

| \$0026                                                | TIM Channel 0<br>Register High (TCH0H)      | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13    | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8    |

|                                                       | See page 132.                               | Reset:          |        |            |           | Indetermina | te after reset |          | l      |          |

| \$0027                                                | TIM Channel 0<br>Register Low (TCH0L)       | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5     | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0    |

|                                                       | See page 132.                               | Reset:          |        | I          |           | Indetermina | te after reset |          |        |          |

|                                                       | TIM Channel 1 Status and                    | Read:           | CH1F   | CHIE       | 0         | MO1A        | EL C1D         | EL C1 A  | TOV4   | CHIMAY   |

|                                                       | Control Register (TSC1)                     | Write:          | : 0    | CH1IE      |           | MS1A        | ELS1B          | ELS1A    | TOV1   | CH1MAX   |

|                                                       | See page 130.                               | Reset:          | 0      | 0          | 0         | 0           | 0              | 0        | 0      | 0        |

| \$0029                                                | TIM Channel 1<br>Register High (TCH1H)      | Read:<br>Write: | Bit 15 | Bit 14     | Bit 13    | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8    |

|                                                       | See page 132.                               | Reset:          |        |            |           | Indetermina | te after reset |          | l .    |          |

| \$002A                                                | TIM Channel 1<br>Register Low (TCH1L)       | Read:<br>Write: | Bit 7  | Bit 6      | Bit 5     | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0    |

|                                                       | See page 132.                               | Reset:          |        |            |           | Indetermina | te after reset |          |        |          |

| \$002B<br>↓<br>\$0035                                 | Unimplemented                               |                 |        |            |           |             |                |          |        |          |

|                                                       |                                             | L               |        |            |           |             |                |          |        |          |

| \$0036 (OSCSTAT)                                      | Oscillator Status Register (OSCSTAT)        | Read:<br>Write: | R      | R          | R         | R           | R              | R        | ECGON  | ECGST    |

|                                                       | See page 96.                                | Reset:          | 0      | 0          | 0         | 0           | 0              | 0        | 0      | 0        |

| \$0037                                                | Unimplemented                               | Read:           |        |            |           |             |                |          |        |          |

|                                                       | •                                           | L               |        |            |           |             |                |          |        |          |

| \$0038 (O                                             | Oscillator Trim Register<br>(OSCTRIM)       | Read:<br>Write: | TRIM7  | TRIM6      | TRIM5     | TRIM4       | TRIM3          | TRIM2    | TRIM1  | TRIM0    |

|                                                       | See page 96.                                | Reset:          | 1      | 0          | 0         | 0           | 0              | 0        | 0      | 0        |

|                                                       |                                             |                 |        | = Unimplem | ented     | R           | = Reserved     | U = Unaf | fected |          |

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 5)

#### Memory Bit 7 5 3 2 Bit 0 Addr. **Register Name** 6 4 1 \$0039 $\downarrow$ Unimplemented \$003B COCO Read: ADC Status and Control AIEN ADCO CH4 CH3 CH2 CH1 CH0 \$003C Register (ADSCR) Write: R See page 45. Reset: 0 0 0 1 1 1 1 1 \$003D Unimplemented Read: ADC Data Register Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 \$003E (ADR) Write: See page 47. Reset: Indeterminate after reset 0 0 0 0 Read: 0 ADC Input Clock Register ADIV2 ADIV1 ADIV0 \$003F (ADICLK) Write: See page 47. Reset: 0 0 0 0 0 0 0 0 Read: SBSW Break Status Register R R R R R R R (BSR) \$FE00 Write: See note 1 See page 137. Reset: 0 1. Writing a 0 clears SBSW. POR PIN COP ILOP ILAD MODRST LVI Read: 0 SIM Reset Status Register \$FE01 (SRSR) Write: See page 117. POR: 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Read: **Break Auxiliary BDCOP** Register (BRKAR) \$FE02 Write: See page 137. Reset: 0 0 0 0 0 0 0 0 Read: **Break Flag Control BCFE** R R R R R R R \$FE03 Register (BFCR) Write: See page 138. Reset: 0 Read: 0 IF5 IF4 IF3 0 IF1 0 0 Interrupt Status Register 1 R R R R R \$FE04 R R R (INT1) Write: See page 77. 0 Reset: 0 0 0 0 0 0 0 IF14 0 0 0 0 0 0 0 Read: Interrupt Status Register 2 R R R R R R R \$FE05 (INT2) Write: R See page 77. Reset: 0 0 0 0 0 0 0 0 Read: 0 0 0 0 0 0 0 IF15 Interrupt Status Register 3 \$FE06 R R R R R R (INT3) Write: R R See page 77. Reset: 0 0 0 0 0 0 0 0 R R R R \$FE07 Reserved R R R R = Unimplemented R = Reserved U = Unaffected

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 5)

# Input/Output (I/O) Section

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 5)

Table 2-1. Vector Addresses

| Vector Priority | Vector           | Address | Vector                                |

|-----------------|------------------|---------|---------------------------------------|

| Lowest          | IF15             | \$FFDE  | ADC conversion complete vector (high) |

| <b>A</b>        |                  | \$FFDF  | ADC conversion complete vector (low)  |

|                 | IF14             | \$FFE0  | Keyboard vector (high)                |

|                 |                  | \$FFE1  | Keyboard vector (low)                 |

|                 | IF13<br>↓<br>IF6 | _       | Not used                              |

|                 | IF5              | \$FFF2  | TIM overflow vector (high)            |

|                 |                  | \$FFF3  | TIM overflow vector (low)             |

|                 | IF4              | \$FFF4  | TIM Channel 1 vector (high)           |

|                 |                  | \$FFF5  | TIM Channel 1 vector (low)            |

|                 | IF3              | \$FFF6  | TIM Channel 0 vector (high)           |

|                 |                  | \$FFF7  | TIM Channel 0 vector (low)            |

|                 | IF2              | _       | Not used                              |

|                 | IF1              | \$FFFA  | IRQ vector (high)                     |

|                 |                  | \$FFFB  | IRQ vector (low)                      |

|                 | _                | \$FFFC  | SWI vector (high)                     |

|                 |                  | \$FFFD  | SWI vector (low)                      |

| <b>Y</b>        |                  | \$FFFE  | Reset vector (high)                   |

| Highest         | _                | \$FFFF  | Reset vector (low)                    |

# 2.5 Random-Access Memory (RAM)

Addresses \$0080–\$00FF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

# NOTE

For correct operation, the stack pointer must point only to RAM locations.

Before processing an interrupt, the central processor unit (CPU) uses five bytes of the stack to save the contents of the CPU registers.

# NOTE

For M6805, M146805, and M68HC05 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

# NOTE

Be careful when using nested subroutines. The CPU may overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

# 2.6 FLASH Memory (FLASH)

This subsection describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from a single external supply. The program and erase operations are enabled through the use of an internal charge pump.

The FLASH memory consists of an array of 4096 or 1536 bytes with an additional 48 bytes for user vectors. The minimum size of FLASH memory that can be erased is 64 bytes; and the maximum size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and erase operations are facilitated through control bits in the FLASH control register (FLCR). Details for these operations appear later in this section. The address ranges for the user memory and vectors are:

- \$EE00 \$FDFF; user memory, 4096 bytes: MC68HC908QY4 and MC68HC908QT4

- \$F800 \$FDFF; user memory, 1536 bytes: MC68HC908QY2, MC68HC908QT2, MC68HC908QY1 and MC68HC908QT1

- \$FFD0 \$FFFF; user interrupt vectors, 48 bytes.

#### NOTE

An erased bit reads as a 1 and a programmed bit reads as a 0. A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

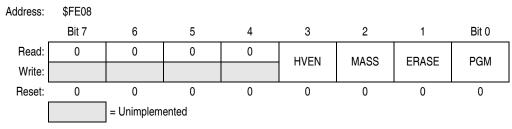

# 2.6.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

# **HVEN** — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or erase operation. It can only be set if either PGM =1 or ERASE =1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

# MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation.

- 1 = Mass erase operation selected

- 0 = Mass erase operation unselected

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### Memory

# **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

# **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

# 2.6.2 FLASH Page Erase Operation

Use the following procedure to erase a page of FLASH memory. A page consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80, or \$XXC0. The 48-byte user interrupt vectors area also forms a page. Any FLASH memory page can be erased alone.

- 1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range of the block to be erased.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>Erase</sub> (minimum 1 ms or 4 ms).

- 7. Clear the ERASE bit.

- 8. Wait for a time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 9. Clear the HVEN bit.

- 10. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, but other unrelated operations may occur between the steps.

# **CAUTION**

A page erase of the vector page will erase the internal oscillator trim values at \$FFC0 and \$FFC1.

In applications that require more than 1000 program/erase cycles, use the 4 ms page erase specification to get improved long-term reliability. Any application can use this 4 ms page erase specification. However, in applications where a FLASH location will be erased and reprogrammed less than 1000 times, and speed is important, use the 1 ms page erase specification to get a shorter cycle time.

# 2.6.3 FLASH Mass Erase Operation

Use the following procedure to erase the entire FLASH memory to read as a 1:

- 1. Set both the ERASE bit and the MASS bit in the FLASH control register.

- Read the FLASH block protect register.

- 3. Write any data to any FLASH address<sup>(1)</sup> within the FLASH memory address range.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time,  $t_{MErase}$  (minimum 4 ms).

- 7. Clear the ERASE and MASS bits.

#### NOTE

Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF).

- 8. Wait for a time,  $t_{NVHL}$  (minimum 100  $\mu$ s).

- 9. Clear the HVEN bit.

- After time, t<sub>RCV</sub> (typical 1 μs), the memory can be accessed in read mode again.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, but other unrelated operations may occur between the steps.

#### CAUTION

A mass erase will erase the internal oscillator trim values at \$FFC0 and \$FFC1.

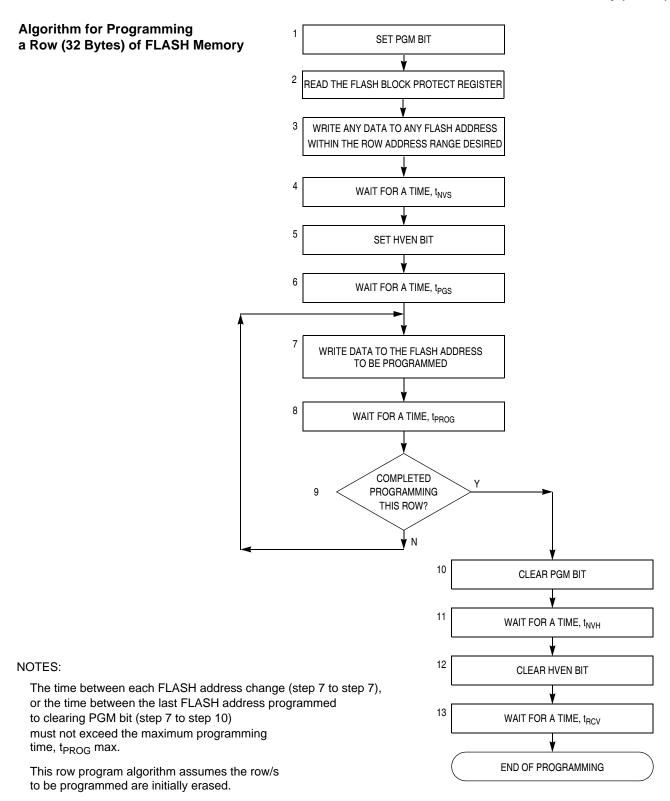

# 2.6.4 FLASH Program Operation

Programming of the FLASH memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0, or \$XXE0. Use the following step-by-step procedure to program a row of FLASH memory

Figure 2-4 shows a flowchart of the programming algorithm.

#### NOTE

Only bytes which are currently \$FF may be programmed.

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range desired.

- 4. Wait for a time,  $t_{NVS}$  (minimum 10  $\mu$ s).

- 5. Set the HVEN bit.

- 6. Wait for a time,  $t_{PGS}$  (minimum 5  $\mu$ s).

- 7. Write data to the FLASH address being programmed<sup>(2)</sup>.

When in monitor mode, with security sequence failed (see 15.3.2 Security), write to the FLASH block protect register instead of any FLASH address.

#### Memory

- 8. Wait for time,  $t_{PROG}$  (minimum 30  $\mu$ s).

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM bit<sup>(1)</sup>.

- 11. Wait for time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{RCV}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

### NOTE

The COP register at location \$FFFF should not be written between steps 5–12, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is programmed.

### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum, see 16.16 Memory Characteristics.

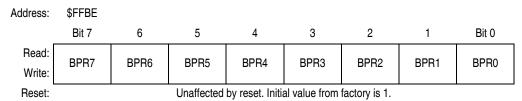

# 2.6.5 FLASH Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

# NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0 s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory. The address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than \$FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF). The FLBPR itself can be erased or programmed only with an external voltage, V<sub>TST</sub>, present on the  $\overline{IRQ}$  pin. This voltage also allows entry from reset into the monitor mode.

<sup>2.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

Figure 2-4. FLASH Programming Flowchart

# 2.6.6 FLASH Block Protect Register

The FLASH block protect register is implemented as a byte within the FLASH memory, and therefore can only be written during a programming sequence of the FLASH memory. The value in this register determines the starting address of the protected range within the FLASH memory.

Write to this register is by a programming sequence to the FLASH memory.

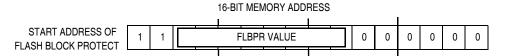

Figure 2-5. FLASH Block Protect Register (FLBPR)

# BPR[7:0] — FLASH Protection Register Bits [7:0]

These eight bits in FLBPR represent bits [13:6] of a 16-bit memory address. Bits [15:14] are 1s and bits [5:0] are 0s.

The resultant 16-bit address is used for specifying the start address of the FLASH memory for block protection. The FLASH is protected from this start address to the end of FLASH memory, at \$FFFF. With this mechanism, the protect start address can be XX00, XX40, XX80, or XXC0 within the FLASH memory. See Figure 2-6 and Table 2-2.

Figure 2-6. FLASH Block Protect Start Address

**Table 2-2. Examples of Protect Start Address**

| BPR[7:0]                  | Start of Address of Protect Range                                                                       |  |  |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| \$00-\$B8                 | The entire FLASH memory is protected.                                                                   |  |  |  |  |  |

| \$B9 ( <b>1011 1001</b> ) | \$EE40 (11 <b>10 1110 01</b> 00 0000)                                                                   |  |  |  |  |  |

| \$BA ( <b>1011 1010</b> ) | \$EE80 (11 <b>10 1110 10</b> 00 0000)                                                                   |  |  |  |  |  |

| \$BB ( <b>1011 1011</b> ) | \$EEC0 (11 <b>10 1110 11</b> 00 0000)                                                                   |  |  |  |  |  |

| \$BC ( <b>1011 1100</b> ) | \$EF00 (11 <b>10 1111 00</b> 00 0000)                                                                   |  |  |  |  |  |

|                           | and so on                                                                                               |  |  |  |  |  |

| \$DE (1101 1110)          | \$F780 (11 <b>11 0111 10</b> 00 0000)                                                                   |  |  |  |  |  |

| \$DF (1101 1111)          | \$F7C0 (11 <b>11 0111 11</b> 00 0000)                                                                   |  |  |  |  |  |

| \$FE (1111 1110)          | \$FF80 (11 <b>11 1111 10</b> 00 0000) FLBPR, internal oscillator trim values, and vectors are protected |  |  |  |  |  |

| \$FF                      | The entire FLASH memory is not protected.                                                               |  |  |  |  |  |

# 2.6.7 Wait Mode

Putting the MCU into wait mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The WAIT instruction should not be executed while performing a program or erase operation on the FLASH, or the operation will discontinue and the FLASH will be on standby mode.

# 2.6.8 Stop Mode

Putting the MCU into stop mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The STOP instruction should not be executed while performing a program or erase operation on the FLASH, or the operation will discontinue and the FLASH will be on standby mode

#### NOTE

Standby mode is the power-saving mode of the FLASH module in which all internal control signals to the FLASH are inactive and the current consumption of the FLASH is at a minimum.