## SKU6704

# TARJETA DE DESARROLLO OPEN4CE10-C ALTERA CYCLONE IV PAQUETE STANDARD

### Descripción:

OpenEP4CE10-C es una placa de desarrollo FPGA que consta de la placa madre DVK600 y la placa central de FPGA Core3S500E.

OpenEP4CE10-C le permite comenzar su diseño con el procesador Nios II de manera fácil y rápida. Open3S500E admite una mayor expansión con varias placas de accesorios opcionales para aplicaciones específicas. El diseño modular y abierto lo hace ideal para iniciar el desarrollo de aplicaciones con los dispositivos FPGA de la serie XILINX Spartan-3E.

|                                                                                     |                                                                                                              |                    |                               |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|

|  | AG Electrónica S.A.P.I. de C.V.<br>República del Salvador N° 20 Segundo Piso<br>Teléfono: (01)55 5130 - 7210 |                    |                               |

| ACOTACIÓN:<br>N/A                                                                   | <a href="http://www.agelectronica.com">http://www.agelectronica.com</a>                                      | ESCALA:<br>N/A     | REALIZO: SAA<br><br>REV: JFRR |

| TOLERANCIA:<br>N/A                                                                  | TARJETA DE DESARROLLO OPEN4CE10-C ALTERA CYCLONE IV<br>PAQUETE STANDARD                                      |                    |                               |

| TOLERANCIA:<br>N/A                                                                  | Fecha:<br>04/03/2021                                                                                         | No. Parte: SKU6704 |                               |

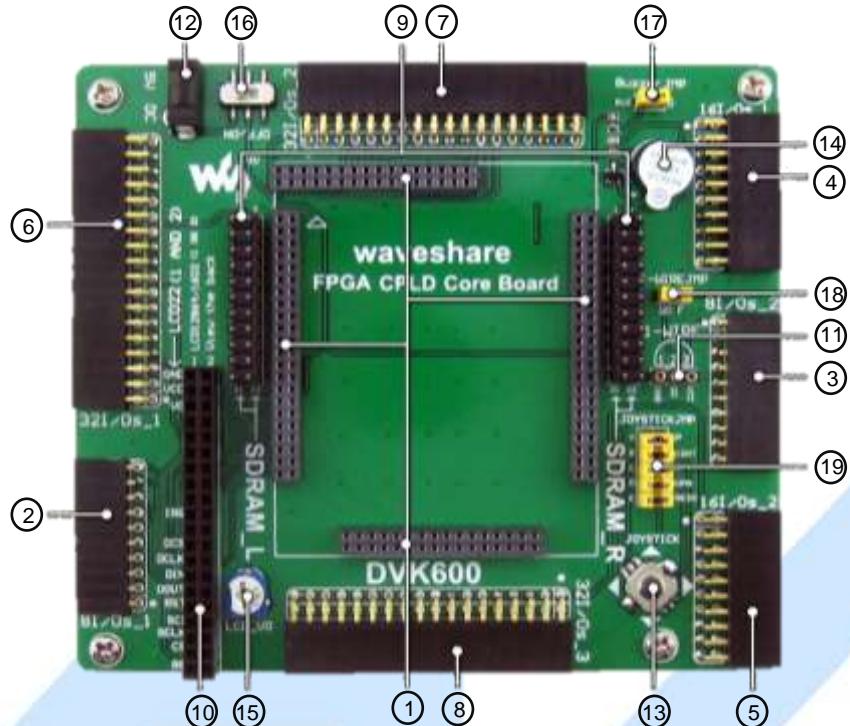

## Especificaciones de la tarjeta madre:

1. **Conector de placa base FPGA CPLD:** para conectar fácilmente placas base que integran un chip FPGA CPLD a bordo

2. **Interfaz 8 E/S s\_1**, para conectar placas / módulos de accesorios

3. **Interfaz 8 E/S s\_2**, para conectar placas / módulos de accesorios

4. **Interfaz 16 E/S s\_1**, para conectar placas / módulos de accesorios

5. **Interfaz 16 E/S s\_2**, para conectar tarjetas / módulos de accesorios

6. **Interfaz 32 E/S s\_1**, para conectar placas / módulos de accesorios

7. **Interfaz 32 E/S s\_2**, para conectar placas / módulos de accesorios

8. **Interfaz 32 E/S s\_3**, para conectar placas / módulos de accesorios

### Todas las interfaces de E / S anteriores:

- Capaces de ser simulado como USART, I2C, SPI, PS / 2, etc.

- Capaces de manejar dispositivos como FRAM, FLASH, USB, Ethernet, etc.

### 9. Interfaz SDRAM

- Para conectar placa de accesorios SDRAM

- También funciona como conectores de expansión de pines FPGA CPLD

### 10. Interfaz LCD, para conectar LCD22, LCD12864, LCD1602

### 11. Interfaz ONE-WIRE: se conecta fácilmente a dispositivos ONE-WIRE (paquete TO-92), como sensor de temperatura (DS18B20), número de registro electrónico (DS2401), etc.

### 12. Toma de 5V

### 13. Joystick: cinco posiciones

### 14. Zumbador

### 15. Potenciómetro: para ajuste de luz de fondo LCD22, o ajuste de contraste LCD12864, LCD1602

### 16. Interruptor de alimentación

### 17. Jumper de zumbador

### 18. Jumper 1-Wire

### 19. Jumper de joystick

### Para Jumpers 17-19:

- Cortocircuite el jumper para conectarlo a las E / S utilizadas en el código de ejemplo

- Abra el jumper para conectarlo a otros pines personalizados a través de cables de puente

El DVK600 admite una amplia gama de placas base diferentes, por lo tanto, algunas de las interfaces pueden no estar conectadas y ser inútiles mientras se conectan a determinadas placas base. Por ejemplo, mientras se conecta a Core3S500E / CoreEP2C8, el '(8) 32I / Os\_3' no está conectado.

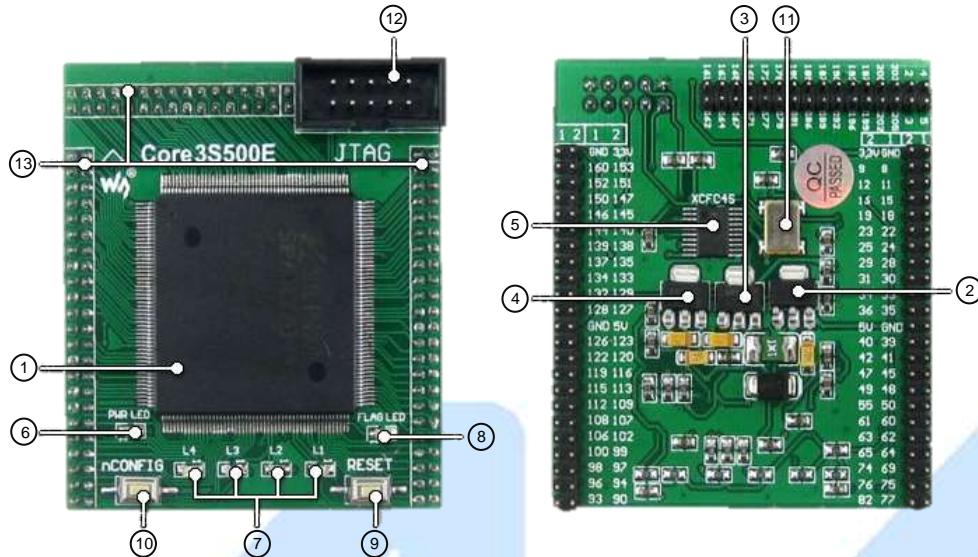

## Especificaciones en el Core3S500E:

1. **XC3S500E:** el dispositivo FPGA XILINX Spartan-3E que cuenta con:

- **Frecuencia de funcionamiento:** 50 MHz

- **Voltaje de funcionamiento:** 1.15 V ~ 3.3 V

- **Encapsulado:** QFP208

- **E / S:** 116

- **LEs:** 500 K

- **RAM:** 360 kb

- **DCMs:** 4

- **Depuración / Programación:** compatible con JTAG

2. **AMS1117-3.3**, regulador de voltaje de 3.3V

3. **AMS1117-2.5**, regulador de voltaje de 2.5V

4. **AMS1117-1.2**, regulador de voltaje de 1.2V

5. **XCF04S**, memoria FLASH serial incorporada, para almacenar código

6. **Indicador de encendido**

7. **LEDs**

8. **Indicador de inicialización FPGA**

9. **Botón de reinicio**

10. **Botón nCONFIG:** para reconfigurar el chip FPGA, el equivalente al reinicio de energía

11. **Oscilador de cristal activo 50M**

12. **Interfaz JTAG:** para depuración / programación

13. **Expansor de pines FPGA, VCC, GND y todos los puertos de E / S son accesibles en conectores de expansión** para una mayor expansión

## Interfaz de depuración / programación

La placa de desarrollo FPGA Open3S500E integra la interfaz JTAG para programación / depuración.

| Pin | Nombre    | Descripción                       |

|-----|-----------|-----------------------------------|

| 1   | TCK       | Señal de reloj                    |

| 2   | GND       | Tierra                            |

| 3   | TDO       | Datos del dispositivo             |

| 4   | VCC(TRGT) | Fuente de alimentación de destino |

| 5   | TMS       | Control de máquina de estado JTAG |

| 6   | NC        | Sin conexión                      |

| 7   | NC        | Sin conexión                      |

| 8   | NC        | Sin conexión                      |

| 9   | TDI       | Datos del dispositivo             |

| 10  | GND       | Tierra                            |

|     |   |    |           |

|-----|---|----|-----------|

| TCK | 1 | 2  | GND       |

| TDO | 3 | 4  | VCC(TRGT) |

| TMS | 5 | 6  | NC        |

| NC  | 7 | 8  | NC        |

| TDI | 9 | 10 | GND       |