# KIT DE TARJETA DE DESARROLLO OPEN3S500E XILINX SPARTAN-3E CON MODULOS DE INTERFACES Y EXPANSIONES

SKU6706

Productos evaluados por

ingenieros calificados

Garantía y

seguridad en

cada producto

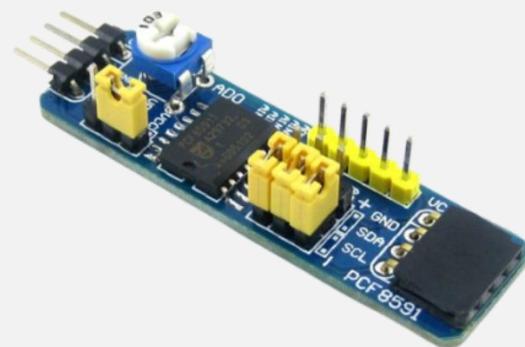

Experiencia de

compra en la

calidad como

sello distintivo

## Descripción

Open3S500E es una Tarjeta de desarrollo FPGA que consta de la Tarjeta madre DVK600 y la Tarjeta central de FPGA Core3S500E. Open3S500E admite una mayor expansión con varios Módulos de accesorios opcionales para aplicaciones específicas. El diseño modular y abierto lo hace ideal para iniciar el desarrollo de aplicaciones con los dispositivos FPGA de la serie XILINX Spartan-3E.

## Contiene

1. Módulo VGA PS2

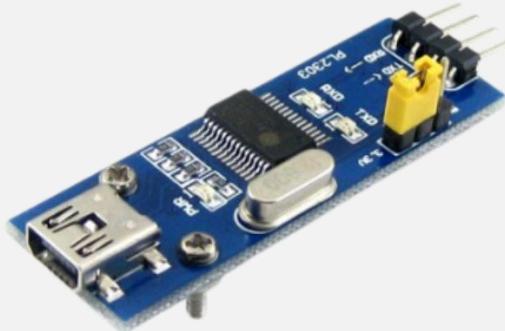

2. Módulo USB UART PL2303 (mini)

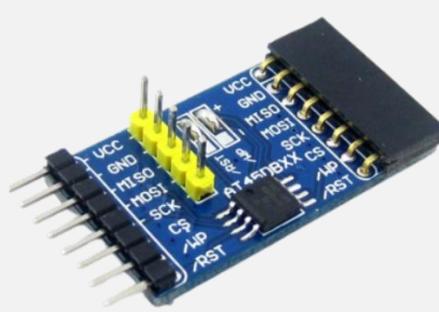

3. Módulo DataFlash AT45DBXX

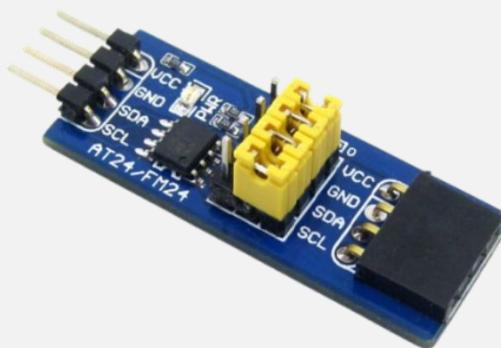

4. Módulo de marco FM24CLXX

5. Módulo USB CY7C68013A (mini)

6. Módulo RTC PCF8563

7. Módulo AD DA PCF8591

8. DS18B20

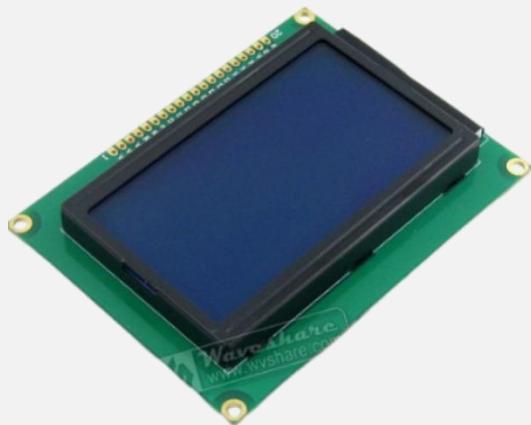

9. LCD12864 (retroiluminación azul de 3.3 V)

10. LCD1602 (retroiluminación azul de 3.3 V)

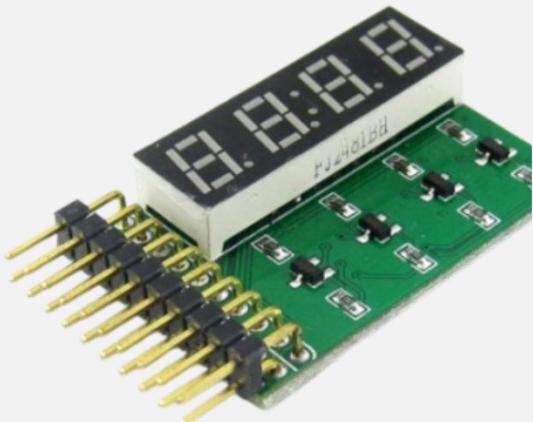

11. Módulo LED de 8 segmentos

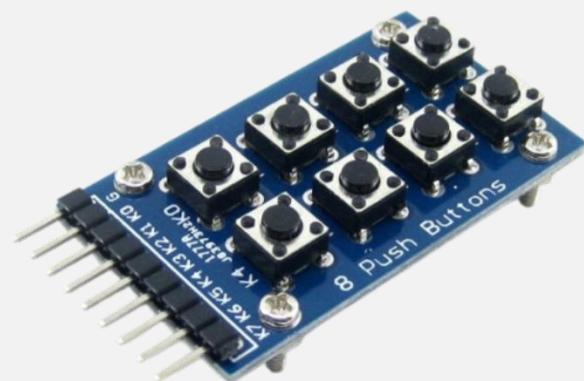

12. Módulo 8 botones pulsadores (2 X4)

13. Módulo 16 botones pulsadores (4 X4)

14. Cable con conector USB tipo A a conector mini-B

1.

5.

2.

6.

3.

7.

4.

8.

9.

12.

10.

13.

11.

14.

## Interfaz Tarjeta Madre DVK600

1. Conector de tarjeta base FPGA CPLD: para conectar fácilmente tarjetas base que integran un chip FPGA CPLD a bordo

2. Interfaz 8 I/Os\_1, para conectar Tarjetas/módulos accesorios

3. Interfaz 8 I/Os\_2, para conectar Tarjetas/módulos accesorios

4. Interfaz 16 I/Os\_1, para conectar Tarjetas/módulos accesorios

5. Interfaz 16 I/Os\_2, para conectar Tarjetas/módulos accesorios

6. Interfaz 32 I/Os\_1, para conectar Tarjetas/módulos accesorios

7. Interfaz 32 I/Os\_2, para conectar Tarjetas/módulos accesorios

8. Interfaz 32 I/Os\_3, para conectar Tarjetas/módulos accesorios

Todas las interfaces de E/S mencionadas son:

- Capaz de ser simulado como USART, I2C, SPI, PS/2, etc.

- Capaz de manejar dispositivos como FRAM, FLASH, USB, Ethernet, etc.

### 9. Interfaz SDRAM

- Para conectar la Tarjeta de accesorios SDRAM

- También funciona como conectores de expansión de pines CPLD FPGA

### 10. Interfaz LCD, para conectar LCD22, LCD12864, LCD1602

11. Interfaz ONE-WIRE: se conecta fácilmente a dispositivos ONE-WIRE (paquete TO-92), como sensor de temperatura (DS18B20), número de registro electrónico (DS2401), etc.

12. Toma de corriente continua de 5 V

13. Joystick: cinco posiciones

14. Zumbador

15. Potenciómetro: para ajuste de retroiluminación LCD22, o ajuste de contraste LCD12864, LCD1602

16. Interruptor de encendido

17. Buzzer (Jumper tipo puente)

18. Cable (Jumper tipo puente)

19. Joystick (Jumper tipo puente)

Para los puentes del 17-19:

- Cortocircuite el puente para conectarlo a las E/S utilizadas en el código de ejemplo

- Abra el puente para conectarlo a otros pines personalizados a través de cables puente.

El DVK600 admite una amplia gama de Tarjetas base diferentes, por lo tanto, es posible que algunas de las interfaces no estén conectadas y no sean útiles al conectarse a determinadas Tarjetas base. Por ejemplo, al conectarse a Core3S500E/CoreEP2C8, "⑧ 32I/Os\_3" no está conectado.

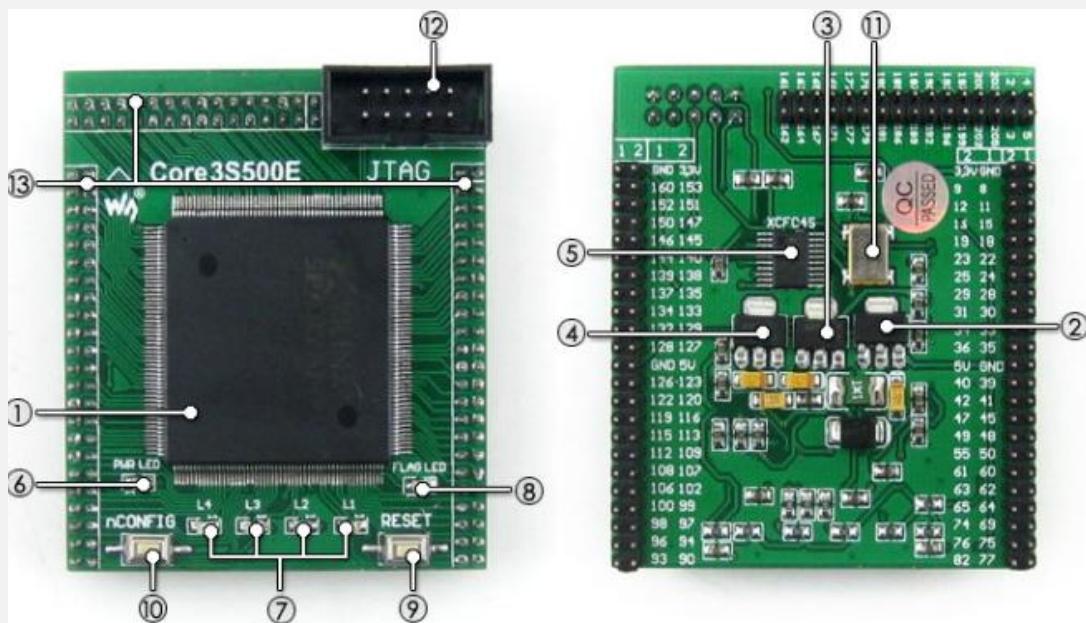

### Interfaz Tarjeta Central Core3S500E

1. XC3S500E: el dispositivo FPGA XILINX Spartan-3E que cuenta con:

- Frecuencia de funcionamiento: 50 MHz

- Voltaje de funcionamiento: 1.15 V ~ 3.3 V

- Encapsulado: QFP208

- E/S: 116

- LEs: 500K

- Memoria RAM: 360 kb

- DCMs: 4

- Depuración/Programación: compatible con JTAG

2. AMS1117-3.3, regulador de voltaje de 3.3 V

3. AMS1117-2.5, regulador de voltaje de 2.5 V

4. AMS1117-1.2, regulador de voltaje de 1.2 V

5. XCF04S, memoria FLASH serial incorporada, para almacenar código

6. Indicador de encendido

7. LED

8. Indicador de inicialización de FPGA

9. Botón de reinicio

10. Botón nCONFIG: para reconfigurar el chip FPGA, el equivalente a reiniciar la energía

11. Oscilador de cristal activo de 50 m

12. Interfaz JTAG: para depuración/programación

13. Los pines expansores del FPGA, VCC, GND y todos los puertos de E/S son accesibles en los conectores de expansión para una mayor expansión.

### Interfaz de programación / depuración

La tarjeta de desarrollo FPGA Open3S500E integra la interfaz JTAG para programación/depuración.

|     |   |    |           |

|-----|---|----|-----------|

| TCK | 1 | 2  | GND       |

| TDO | 3 | 4  | VCC(TRGT) |

| TMS | 5 | 6  | NC        |

| NC  | 7 | 8  | NC        |

| TDI | 9 | 10 | GND       |

### Fotos

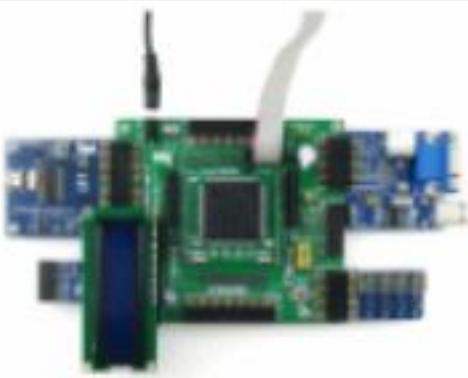

Tarjeta Madre DVK600

Tarjeta Central Core3S500E

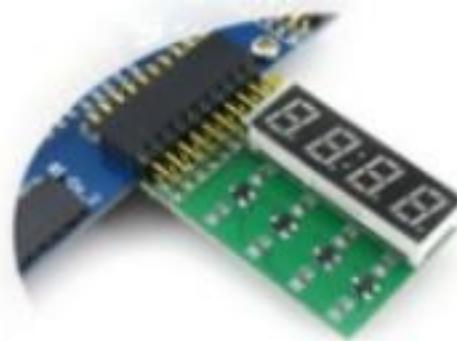

Conexión a LCD1602

Conexión a la placa RS232

Conexión a 8 pulsadores

Conexión al teclado 4x4

Conexión a la placa DataFlash

Conexión a la placa USB

CY7C68013A

Conexión a varios periféricos

Conexión a LCD12864

Conexión a la placa USB UART

Conexión a la placa LED 8 SEG

Conexión a la placa EEPROM

Varios periféricos conectados a una

interfaz

Conexión a placa PS2 VGA

Conexión a cualquier placa de

accesorios que necesite

### Recursos para el desarrollo:

- Software relacionado (Xilinx ISE 12: compatible con WinXP/Win7, no compatible con Win8 )

- Código de demostración (Verilog, VHDL)

- Esquema (PDF)

- Documentación de desarrollo de FPGA

Enlace: [www.waveshare.com/wiki/Open3S500E](http://www.waveshare.com/wiki/Open3S500E)

AG Electrónica SAPI de CV

República de El Salvador 20 Piso 2,

Centro Histórico, Centro, 06000

Ciudad de México, CDMX

Teléfono: 55 5130 7210

Realizó Alan Huerta Zavala

Revisó Ing. Jessica López Morales

Fecha 14/11/2024