# XD74LS06 DIP14 XL74LS06 SOP14

### 1 Features

- · Convert TTL Voltage Levels to MOS Levels

- · High Sink-Current Capability

- Input Clamping Diodes Simplify System Design

- Open-Collector Driver for Indicator Lamps and Relays

- Inputs Fully Compatible With Most TTL Circuits

- On Products Compliant to MIL-PRF-38535, All Parameters Are Tested Unless Otherwise Noted.

On All Other Products, Production Processing Does Not Necessarily Include Testing of All Parameters.

# 2 Applications

- · Factory Automation

- Building Automation

- · Line Drivers

- · Electronic Point of Sale

- · Desktop or Notebook PCs

# 3 Description

The XD74LS06 devices feature high-voltage, open-collector outputs to interface with high-level circuits (such as MOS), or for driving high-current loads, and also are characterized for use as inverter buffers for driving TTL inputs. The XD74LS06 devices have a rated output voltage of 30 V.

### 4 Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)    |

|-------------|-----------|--------------------|

| 54LS06      | CDIP (14) | 19.50 mm × 6.92 mm |

| 54LS06      | LCCC (20) | 8.89 mm × 8.89 mm  |

| XL746S06    | SOIC (14) | 8.65 mm × 3.91 mm  |

| XL74LS06-SS | SSOP (14) | 5.30 mm × 6.20 mm  |

| XD74LS06    | PDIP (14) | 19.30 mm × 6.35 mm |

| XD74LS06S   | SOP (14)  | 5.30 mm × 10.20 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

### Logic Diagram (Positive Logic)

$$1A \xrightarrow{1} 2 \xrightarrow{2} 1Y$$

$$2A \xrightarrow{3} 2 \xrightarrow{4} 2Y$$

$$3A \xrightarrow{5} 2 \xrightarrow{6} 3Y$$

$$4A \xrightarrow{9} 2 \xrightarrow{8} 4Y$$

$$5A \xrightarrow{11} 2 \xrightarrow{10} 5Y$$

$$6A \xrightarrow{13} 2 \xrightarrow{12} 6Y$$

Pin numbers shown are for the D, DB, J, N, and NS packages.

# 5 Pin Configuration and Functions

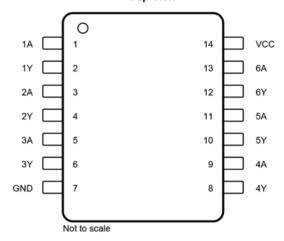

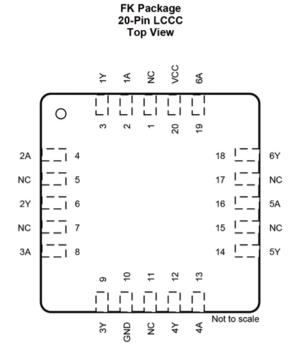

D, DB, J, N, and NS Package 14-Pin SOIC, SSOP, CDIP, PDIP, and SOP Top View

### **Pin Functions**

|                 | PIN                            |                        |     |                        |

|-----------------|--------------------------------|------------------------|-----|------------------------|

| NAME            | SOIC, SSOP,<br>CDIP, PDIP, SOP | LCCC                   | I/O | DESCRIPTION            |

| 1A              | 1                              | 2                      | I   | 1A Input               |

| 1Y              | 2                              | 3                      | 0   | 1Y Output              |

| 2A              | 3                              | 4                      | I   | 2A Input               |

| 2Y              | 4                              | 6                      | 0   | 2Y Output              |

| 3A              | 5                              | 8                      | - 1 | 3A Input               |

| 3Y              | 6                              | 9                      | 0   | 3Y Output              |

| 4A              | 9                              | 13                     | I   | 4A Input               |

| 4Y              | 8                              | 12                     | 0   | 4Y Output              |

| 5A              | 11                             | 16                     | I   | 5A Input               |

| 5Y              | 10                             | 14                     | 0   | 5Y Output              |

| 6A              | 13                             | 19                     | - 1 | 6A Input               |

| 6Y              | 12                             | 18                     | 0   | 6Y Output              |

| GND             | 7                              | 10                     | _   | Ground                 |

| NC              | _                              | 1, 5, 7,<br>11, 15, 17 | _   | No internal connection |

| V <sub>CC</sub> | 14                             | 20                     | _   | Power pin              |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                             | MIN | MAX | UNIT |

|-------------------------------------------------------------|-----|-----|------|

| Supply voltage, V <sub>CC</sub>                             |     | 7   | V    |

| Input voltage, V <sub>I</sub> <sup>(2)</sup>                |     | 7   | V    |

| Output voltage, V <sub>O</sub> (XD74LS06) <sup>(2)(3)</sup> |     | 30  | V    |

| Absolute maximum junction temperature, T <sub>J</sub>       |     | 150 | °C   |

| Storage temperature, T <sub>stg</sub>                       | -65 | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to GND.

# 6.2 ESD Ratings

|                                |                         |                                                                                | VALUE | UNIT        |

|--------------------------------|-------------------------|--------------------------------------------------------------------------------|-------|-------------|

| V Floating static displacement |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±500  | \ \ \ \ \ \ |

| V <sub>(ESD)</sub>             | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±2000 | V           |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                                 |                                          |          | MIN | NOM | MAX | UNIT |

|---------------------------------|------------------------------------------|----------|-----|-----|-----|------|

| V <sub>CC</sub>                 | C Supply voltage                         |          | 4.5 | 5   | 5.5 | V    |

| V <sub>IH</sub>                 | High-level input voltage                 |          | 2   |     |     | V    |

| V <sub>IL</sub>                 | Low-level input voltage                  |          |     |     | 0.8 | V    |

| V <sub>OH</sub>                 | High-level output voltage (XD74LS06)     |          |     |     | 30  | V    |

|                                 | I <sub>OL</sub> Low-level output current | XD74LS06 |     |     | 30  | A    |

| OL                              |                                          | XL74LS06 |     |     | 40  | mA   |

| T <sub>A</sub> Operating free-a | 0                                        | XD74LS06 | -55 |     | 125 | °C   |

|                                 | Operating free-air temperature           | XL74LS06 | 0   |     | 70  | °C   |

<sup>(1)</sup> All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. See the *Implications of Slow or Floating CMOS Inputs* application report.

<sup>(3)</sup> This is the maximum voltage that must be applied to any output when it is in the off state.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Tested on N package

#### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | XD74LS06 |           |          |          |      |

|-------------------------------|----------------------------------------------|----------|-----------|----------|----------|------|

|                               |                                              | D (SOIC) | DB (SSOP) | N (PDIP) | NS (SOP) | UNIT |

|                               |                                              | 14 PINS  | 14 PINS   | 14 PINS  | 14 PINS  |      |

| R <sub>eJA</sub>              | Junction-to-ambient thermal resistance       | 85.8     | 97.4      | 50.2     | 82.8     | °C/W |

| R <sub>0</sub> JC(top)        | Junction-to-case (top) thermal resistance    | 44       | 49.8      | 37.5     | 40.9     | °C/W |

| R <sub>eJB</sub>              | Junction-to-board thermal resistance         | 40.3     | 44.5      | 30       | 41.4     | °C/W |

| ΨЈТ                           | Junction-to-top characterization parameter   | 11.1     | 16.5      | 22.3     | 12.4     | °C/W |

| ΨЈВ                           | Junction-to-board characterization parameter | 40.1     | 44        | 29.9     | 41.1     | °C/W |

| R <sub>eJC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | _        | _         | _        | _        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report

#### 6.5 Electrical Characteristics

over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                       | TEST CONDITIONS <sup>(1)</sup>                                                  |                                   | MIN | TYP <sup>(2)</sup> | MAX  | UNIT |

|---------------------------------|---------------------------------------------------------------------------------|-----------------------------------|-----|--------------------|------|------|

| V <sub>IK</sub>                 | $V_{CC} = MIN, I_I = -12 \text{ mA}$                                            |                                   |     |                    | -1.5 | V    |

| I <sub>OH</sub>                 | V <sub>CC</sub> = MIN, V <sub>IL</sub> = 0.8 V, V <sub>OH</sub> = 30 V, XD74LS0 | 06 XL74LS06                       |     |                    | 0.25 | mA   |

|                                 |                                                                                 | I <sub>OL</sub> = 16 mA           |     | 0.25               | 0.4  |      |

| $V_{OL}$ $V_{CC} = MIN, V_{IH}$ | V <sub>CC</sub> = MIN, V <sub>IH</sub> = 2 V                                    | I <sub>OL</sub> = 30 mA           |     |                    | 0.7  | -    |

|                                 |                                                                                 | I <sub>OL</sub> = 40 mA, SN74LS06 |     |                    | 0.7  |      |

| I <sub>I</sub>                  | V <sub>CC</sub> = MAX, V <sub>I</sub> = 7 V                                     |                                   |     |                    | 1    | mA   |

| I <sub>IH</sub>                 | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.4 V                                   |                                   |     |                    | 20   | μΑ   |

| I <sub>IL</sub>                 | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4 V                                   |                                   |     |                    | -0.2 | mA   |

| I <sub>CCH</sub>                | V <sub>CC</sub> = MAX                                                           |                                   |     |                    | 18   | mA   |

| I <sub>CCL</sub>                | V <sub>CC</sub> = MAX                                                           |                                   |     |                    | 60   | mA   |

<sup>(1)</sup> For conditions shown as MIN or MAX, use the appropriate value specified under Recommended Operating Conditions.

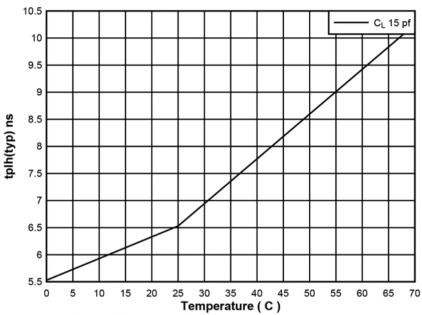

### 6.6 Switching Characteristics

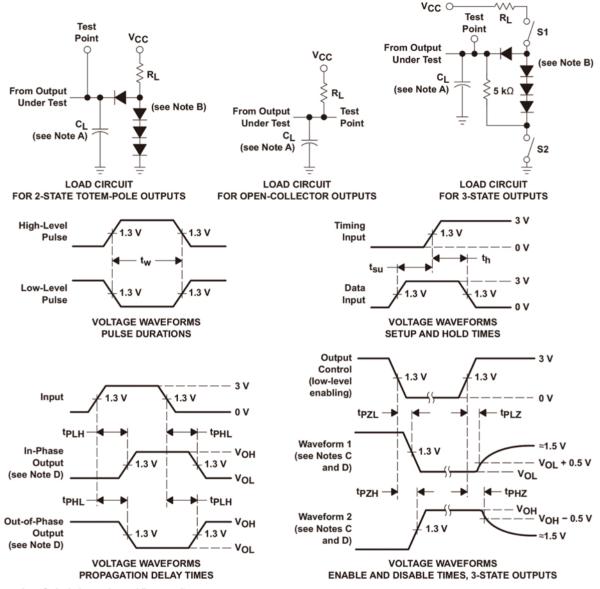

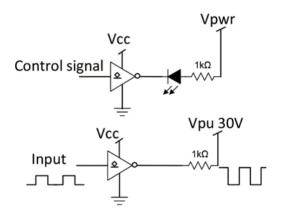

$V_{CC} = 5 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$  (see Figure 2)

| PARAMETER        | TEST CONDITIONS                                                    | MIN | TYP MAX | UNIT |

|------------------|--------------------------------------------------------------------|-----|---------|------|

| t <sub>PLH</sub> | From A (input) to Y (output), $R_L$ = 110 $\Omega$ , $C_L$ = 15 pF | 7   | 15      |      |

| t <sub>PHL</sub> | From A (input) to Y (output), $R_L$ = 110 $\Omega$ , $C_L$ = 15 pF | 10  | 20      | ns   |

<sup>(2)</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ , and  $T_A = 25^{\circ}\text{C}$ .

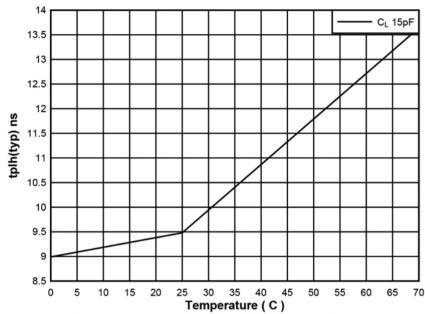

# 6.7 Typical Characteristics

Figure 1. Propagation Delay vs Temperature

#### 7 Parameter Measurement Information

- A.  $C_L$  includes probe and jig capacitance.

- B. All diodes are 1N3064 or equivalent.

- C. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.

- D. S1 and S2 are closed for t<sub>PLH</sub>, t<sub>PHL</sub>, t<sub>PHZ</sub>, and t<sub>PLZ</sub>; S1 is open and S2 is closed for t<sub>PZH</sub>; S1 is closed and S2 is open for t<sub>PZL</sub>.

- E. Phase relationships between inputs and outputs have been chosen arbitrarily for these examples.

- F. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_O \approx 50 \Omega$ ,  $t_i \leq$  1.5 ns,  $t_i \leq$  2.6 ns.

- G. The outputs are measured one at a time, with one input transition per measurement.

Figure 2. Load Circuits and Voltage Waveforms

# 8 Detailed Description

#### 8.1 Overview

The XD74LS06 devices are open-collector output inverters. The maximum sink current for the XD74LS06 device is 30 mA, and for the XD74LS06 device it is 40 mA. These devices are compatible with most TTL families. Inputs are diode-clamped to minimize transmission effects, which simplifies design. Typical power dissipation is 175 mW, and average propagation delay time is 8 ns.

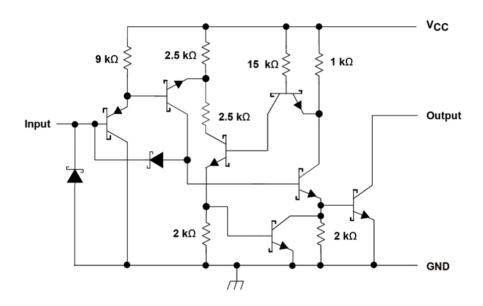

# 8.2 Functional Block Diagram

### 8.3 Feature Description

The XD74LS06 devices can convert most TTL voltage circuit voltage level to MOS levels. The devices have high sink-current capability of up to 40 mA. The open-collector driver can be used for typical applications including Indicator lamps and relays.

#### 8.4 Device Functional Modes

Table 1 lists the functional modes of the XD74LS06 devices.

Table 1. Function Table

| INPUT<br>A | OUTPUT<br>Y |

|------------|-------------|

| Н          | L           |

| L          | Hi-Z        |

# 9 Application and Implementation

### 9.1 Application Information

The open-collector device is suitable for high-drive and high-voltage translation applications.

### 9.2 Typical Application

Figure 3. Application Schematic

#### 9.2.1 Design Requirements

The XD74LS06 are open-collector devices which can sink current (up to 40 mA on XD74LS06) The devices can be used in applications such as LED drivers and voltage translation using pullup resistors.

### 9.2.2 Detailed Design Procedure

- 1. Recommended input conditions:

- Specified high and low levels. See ( $V_{IH}$  and  $V_{IL}$ ) in the *Recommended Operating Conditions*.

- Inputs are overvoltage tolerant allowing them to go as high as 5.5 V at any valid V<sub>CC</sub>.

- 2. Recommended output conditions:

- Load currents must not exceed (Io max) per output.

- Outputs can be pulled up to 30 V.

# Typical Application (continued)

### 9.2.3 Application Curve

Figure 4. Propagation Delay vs Temperature

# 10 Power Supply Recommendations

The power supply can be any voltage between the minimum and maximum supply voltage rating located in the *Recommended Operating Conditions*.

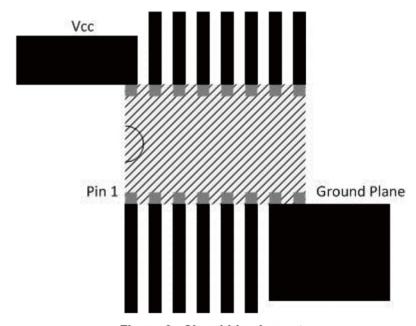

Each  $V_{CC}$  pin must have a good bypass capacitor to prevent power disturbance. For devices with a single supply, TI recommends a 0.1- $\mu$ F capacitor, and if there are multiple  $V_{CC}$  pins, then TI recommends a 0.01- $\mu$ F or 0.022- $\mu$ F capacitor for each power pin. It is ok to parallel multiple bypass capacitors to reject different frequencies of noise. 0.1- $\mu$ F and 1- $\mu$ F capacitors are commonly used in parallel. The bypass capacitor must be installed as close to the power pin as possible for best results.

# 11 Layout

### 11.1 Layout Guidelines

When using multiple bit logic devices, inputs must not ever float. In many cases, functions or parts of functions of digital logic devices are unused; for example, when only two inputs of a triple-input and gate are used or only 3 of the 4 buffer gates are used. Such input pins must not be left unconnected because the undefined voltages at the outside connections result in undefined operational states. The following rules must be observed under all circumstances. All unused inputs of digital logic devices must be connected to a high or low bias to prevent them from floating. The logic level that must be applied to any particular unused input depends on the function of the device. Generally they are tied to GND or  $V_{CC}$  whichever make more sense or is more convenient. The recommends keeping the signal lines as short and as straight as possible (see Figure 6). Incorporation of microstrip or stripline techniques are also recommended when signal lines are more than 1" long. These traces must be designed with a characteristic impedance of either 50  $\Omega$  or 75  $\Omega$  as required by the application.

### 11.2 Layout Examples

Figure 5. Layout Schematic

Figure 6. Signal Line Layout

以上信息仅供参考. 如需帮助联系客服人员。谢谢 XINLUDA